論文

## ダイオードの接合容量を考慮した Cockcroft-Walton 回路における 昇圧比向上および力率改善

正 員 南 政孝\*a) 准 員 伊藤 健\*\* 正 員 茂木 進一\* 正 員 道平 雅一\*

# Boost Ratio and Power Factor Improvement in Cockcroft-Walton Circuit with Diode Junction Capacitor

Masataka Minami\*a), Member, Takeshi Ito\*\*, Associate, Shin-ichi Motegi\*, Member, Masakazu Michihira\*, Member

(2016年4月6日受付, 2016年7月9日再受付)

The Cockcroft-Walton (CW) circuit, which is well known as a high step-up rectifier, is used in a lot of systems. It is considered that the boost ratio of the circuit decreases according to the load current and the diode junction capacitor. In addition, it is necessary for these rectifiers to use some power factor correctors. This paper investigates the circuit which adds an input inductor. The proposed circuit is focused on *LC* resonance between the input inductor and the diode junction capacitors. It is numerically and experimentally clarified that the *LC* resonance improves the boost ratio and the power factor.

キーワード:Cockcroft-Walton 回路,昇圧比,力率,接合容量,*LC* 共振,高周波 **Keywords:** Cockcroft-Walton circuit, boost ratio, power factor, junction capacitor, *LC* resonance, high frequency

### 1. はじめに

電気自動車や燃料電池を用いたシステムなどには、高電圧が用いられているため、システム内に高昇圧比を持った電力変換器が必要とされている(\*\*)。このような背景を受けて、高昇圧比電力変換器の研究開発が見直されつつある(\*\*)。その中でも、古くから高昇圧比電力変換器として Cockcroft-Walton 回路(\*\*)(以下、CW 回路とする)が広く用いられている。CW 回路は、回路構成が簡易であり、能動スイッチを必要としないという利点がある。さらに、それぞれのコンデンサに等電圧で充電される特性を利用して、電気二重層キャパシタの充電回路としても注目されている(\*\*)。しかしながら、負荷電流による昇圧比の減少(\*\*)(\*\*)(\*\*)や電源周波数の制約から、X 線照射装置、粒子加速器、絶縁試験装置など

の小電力機器を中心に用いられていた。また、CW回路をはじめとするダイオードを用いた整流器では、力率が悪いため、新たに力率改善回路を必要とすることが多い。

昇圧比の向上には、電源周波数の高周波化や段数の増加(5)、回路構成の工夫(7)~(10)、パラメータの調整(11)などが提案されている。これまでは半導体素子の制約により、電源周波数が1kHz以下であった。昨今の半導体技術の進歩により、高速動作可能な半導体素子を用いることで、1kHz以上で使用されてきている。さらに、従来、昇圧比の減少は負荷電流が主原因であると言われていた(5)(6)。しかしながら、負荷電流が流れない無負荷状態においても昇圧比が減少することを著者らは示すとともに、その主原因がダイオードの接合容量であることを理論的に明らかにした(12)。

本論文は文献(12)の続報であり、昇圧比の向上および力率の改善を目的とした回路を提案および検証する。実用回路では、入力として方形波が用いられることが多いが、方形波に含まれる奇数次高調波の影響が無視できない(13)。そこで本論文では、方形波入力を用いる前段階として、正弦波入力の場合における提案回路の効果や影響を検証する。改善回路は、従来のCW回路の入力端にインダクタを挿入したもので、インダクタとダイオードの接合容量の共振を利用する。昇圧比を減少させる原因であるダイオードの接合容量をあえて利用することによって、昇圧比の向上が達

a) Correspondence to: Masataka Minami. E-mail: minami@kobe-kosen.ac.jp

<sup>\*</sup> 神戸市立工業高等専門学校 電気工学科 〒 651-2194 神戸市西区学園東町 8-3 Kobe City College of Technology 8-3, Gakuenhigashi, Nishi-ku, Kobe 651-2194, Japan

<sup>\*\*</sup> 長岡技術科学大学工学部 電気電子情報工学課程 〒 940-2188 長岡市上富岡町 1603-1 Nagaoka University of Technology 1603-1, Kamitomioka, Nagaoka 940-2188, Japan

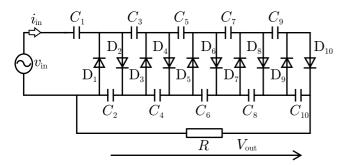

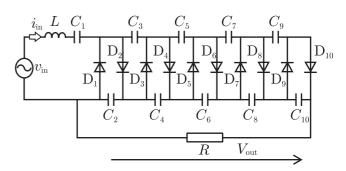

Fig. 1. 5-stage Cockcroft-Walton circuit.

成されることを示す。さらに、挿入したインダクタにより、 高力率化が可能であることを報告する。

#### 2. 従来の CW 回路と提案回路

本章では、従来のCW回路における回路動作を示す。まずはじめに、従来のCW回路の構成を示し、本論文で用いる変数やパラメータの設定を述べる。次に、CW回路の定常動作である実験波形の一例を示し、動作の説明を行なう。この定常動作をもとに、CW回路の問題点について明らかにする。最後に提案回路を示し、その効果について述べる。

〈2・1〉 対象とする回路とその設定 本節では、対象とする従来の CW 回路とその設定について説明する。Fig.1 に、5 段の CW 回路を示す。コンデンサとダイオードが交互に接続されており、入力電圧の極性が反転することにより、ダイオードの導通と非導通が切り替わる。理想的には、コンデンサ  $C_1$  に入力電源電圧の振幅値に等しい電圧が充電され、それ以外のコンデンサに 2 倍の電圧が充電される。したがって、5 段の CW 回路は理論上、入力電源電圧の 10 倍の出力電圧が得られる。しかしながら、負荷電流により昇圧比が減少することが知られている  $^{(5)(6)}$ 。 さらに著者らは、文献 (12) において、ダイオードの接合容量により 5 段の CW 回路の入出力比  $V_{\text{out}}/V_{\text{in}}$  が以下のように表されることを理論的に示した。

$$V_{\text{out}}/V_{\text{in}} = 10 \cdot \frac{1 + 14(C_{\text{T}}/C) + 59.2(C_{\text{T}}/C)^2}{1 + 55(C_{\text{T}}/C) + 495(C_{\text{T}}/C)^2} \cdot \dots (1)$$

ここで、 $C_T$  はダイオードの接合容量、C は CW 回路を構成するコンデンサ容量を表しており、 $(C_T/C)^3$  以上の項は充分小さいので無視している。さらに、CW 回路をはじめとするダイオードを用いた整流器では、入力電流の高調波や低力率と言った問題がある。特に CW 回路の場合、ダイオードが逆バイアス時には、ダイオードの接合容量の影響が顕著に現れる。そのため、力率の改善が必要となってくる。

次に、Fig. 1 におけるパラメータや変数をまとめる。入力電源の電流電圧を $i_{\rm in}$ 、 $v_{\rm in}=V_{\rm in}\sin 2\pi ft$  ( $V_{\rm in}=100\,{\rm V}$ 、 $f=100\,{\rm kHz}$ ) とし、入力電源の設定値は本論文中で同じであるとする。 さらに、各コンデンサの電圧を $v_{C_i}$  ( $i=1,2,\cdots,10$ ) とし、出力端の負荷にかかる電圧を $v_{\rm out}$  とする。また、コンデンサ $C_i$  ( $i=1,2,\cdots,10$ ) の容量は全て等しく、 $C=4700\,{\rm pF}$ とおく。実験においてコンデンサは、耐圧  $3\,{\rm kV}$  のセラミッ

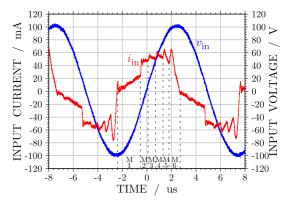

Fig. 2. Input current and voltage waveforms in Fig. 1.

クコンデンサを使用する $^{\dagger}$ 。ダイオードは、Ultra-FRD の MUR460(600 V, 4 A)を 2 直列に接続して用いる。負荷は 純抵抗 R を用いる。

続いて,入出力電圧に対する昇圧比について述べる。出力電圧  $v_{\rm out}$  は整流されて直流に変換されるので,時間平均電圧  $V_{\rm out} = \langle v_{\rm out} \rangle^{\dagger\dagger}$  を出力電圧値と定義する。そして,CW回路の昇圧比 $\alpha$  を  $v_{\rm in}$  の振幅  $V_{\rm in}$  と出力電圧の時間平均電圧  $V_{\rm out}$  から, $\alpha = V_{\rm out}/V_{\rm in}$  と定義する。

最後に、力率について述べる。本論文中では力率として、総合力率 TPF(Total Power Factor) (14)を用いる。総合力率の計算は、TPF =  $\langle v_{\rm in} i_{\rm in} \rangle / (V_{\rm in}^{\rm rms} I_{\rm in}^{\rm rms})$  と定義する。ここで、上添字の rms は実効値を意味する。本論文では、昇圧比  $\alpha$  と総合力率 TPF を従来回路および提案回路の評価指標として用いる。

**〈2・2〉 定常動作特性** 本節では、Fig. 1 における定常動作の説明をするとともに、その結果に基づく従来の CW 回路の問題点について明らかにする。

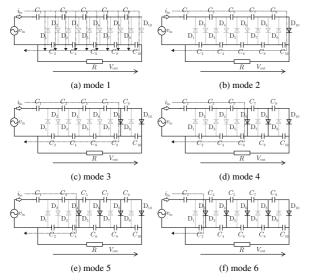

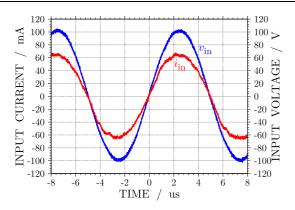

Fig. 2 に,負荷抵抗  $R=250\,\mathrm{k}\Omega$  とした場合の Fig. 1 における入力電流,入力電圧の実験結果の一例を示す。ここで,赤色の実線が入力電流波形,青色の実線が入力電圧波形を表している。定常動作を説明するため,入力電流の正の半周期に対して,ダイオードの導通と非導通によるモード切り替えを mode 1 (M1)  $\sim$  mode 6 (M6) と定義し,Fig. 2 中に破線で示す。Fig. 2 における各々のモードについて説明する。Fig. 3 にモード毎の等価回路を示す。破線は,電流が主に流れる箇所を示しており,負荷へ流れる電流はどのモードにおいても流れているので省略している。

mode 1 は、ダイオードが全て非導通となっている。そのため、Fig. 3(a) 内の電流が主に流れるループが形成されない。そこで支配的になるのは、ダイオードの逆バイアス時に発生する接合容量である。全てのダイオードに逆バイアスが印加されているので、全てのダイオードを等価的に接合容量であるとみなす。Fig. 4 にその等価回路を示す。こ

〈 〉を次のように定義する。

$$\langle x(t) \rangle = \frac{1}{T} \int_{t_0}^{t_0+T} x(t) dt$$

<sup>†</sup> 高耐圧のコンデンサを使用するため、小容量に設定している。

$<sup>^{\</sup>dagger\dagger}$  ここで,周期  $^{T}$  の時間波形 x(t) に対して,時間平均の演算として,

Fig. 3. Equivalent circuit of every mode.

こで、ダイオードの接合容量を $C_T$ としている。入力端から見た全インピーダンスの計算のため、負荷抵抗が大きく出力端が開放であると仮定する。さらに、ダイオードのデータシートから $C_T \ll C$ である。以上の近似を用いることによってFig.4の電源から見た全インピーダンスは $10C_T$ となる。Fig.3(a) の mode 1 では、このダイオードの接合容量に入力電流が流れていることを表している。ここで、ダイオードの接合容量に入力電流が流れていることを概算にて示す。Fig.2 の mode 1 において、入力電流は直線的に増加しているので、入力される電荷 $Q_{in}$  は以下の通りとなる。

$$Q_{\rm in} = \int_{-2.4}^{-0.5} i_{\rm in} \, dt \approx 19 \, \rm nC \, \cdots$$

(2)

そのうち、負荷抵抗側に流れる電荷は、約 500 V/250 k $\Omega$ -1.9 us より約 4 nC 流れることになる。そのため、CW 回路内には、約 15 nC の電荷が蓄積される。一方、ダイオードは出力電圧を 10 直列しているので、1 つあたりにかかる電圧は約 50 V となる。そして、データシートよりダイオードの接合容量を  $C_{\rm T} \approx 30\,{\rm pF}$  とすると、ダイオードの接合容量に充電される電荷  $Q_{\rm T,all}$  は以下のように計算できる。

$$Q_{\text{T,all}} = \sum_{i=1}^{10} C_{\text{T}} v_{C_i} \approx 15 \,\text{nC} \quad \cdots \qquad (3)$$

以上のことから、mode 1 において、入力電流はダイオードの接合容量に流れていると言える。

Fig. 3 の mode 2~mode 6 では,右端のダイオード  $(D_{10})$  から順番に導通していき,電流が流れる。mode 2 では,ダイオード  $D_{10}$  が導通して, $C_1$ ~ $C_{10}$  が直列に接続されたコンデンサに充電される。mode 3 では,ダイオード  $D_9$  と  $D_{10}$  が導通する。ここで,ダイオード  $D_9$  が導通することによって, $C_9$  と  $C_{10}$  にかかる電圧が等しくなっているので,ダイオード  $D_{10}$  には,ほとんど電流が流れていない。同様の動作が mode 4~mode 6 に生じている。これらのことから,mode 2~mode 6 のそれぞれにおいて,モードが切り替わ

Fig. 4. Equivalent circuit of Fig. 3(a).

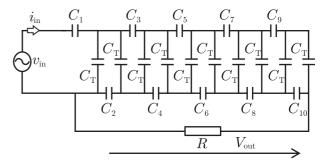

Fig. 5. Proposed 5-stage CW circuit with L.

る時間が短いので、ダイオードに電流が瞬間的に流れると考えられる。そのため、Fig.2における入力電流  $i_{in}$  の波形に 5 つのピークが現れていることが分かる。

以上の定常動作特性から、従来の CW 回路では、各々のコンデンサおよびダイオードの接合容量への充電が必要になる。そのため、入力側からは容量性負荷のように見える。その結果、従来の CW 回路は低力率であるということが問題である。さらに、短時間にパルス的に電流が流れることから、入力電流の高調波成分が多くなってしまう。実際、Fig. 2 の TPF = 50%、THD = 29%である。

最後に、定常動作におけるダイオードの非導通の時間に注目する。ダイオードが非導通、すなわち逆バイアス時には、ダイオードが接合容量として等価的に考えることができる。著者らは、ダイオードの接合容量における充電および放電により昇圧比が減少することを示している(12)。定常動作の結果から、ダイオードが非導通になっている期間が長いことが、昇圧比を減少させるという問題である。

《2·3》 提案回路 本節では、本論文における提案回路 を示し、前節の問題を解決するための効果について述べる。 Fig. 5 に提案回路を示す。従来の CW 回路の入力端にイ

Tig.5 に提来回路をがす。此本のとW 回路の人力場にインダクタを挿入した回路である。インダクタを挿入することによって、前節に述べたパルス的な電流を滑らかにすることを考えている。さらに、その影響によりダイオード電流が流れる時間を緩やかにする効果を期待している。ダイオード電流の時間を長くすることによって、入力された電流を有効に負荷へ送ることができる。つまり力率や昇圧比が改善されるのではないかと考えている。

また, Fig. 4 のような mode 1 においてダイオードの接合 容量への充放電が生じることを利用する。インダクタを挿

入することで,入力側からは LC フィルタが接続されているように見える。この LC フィルタに生じる直列共振を用いることで,昇圧比が向上するのではないかと考えている。提案回路のデメリットは,回路の大型化が挙げられるが,今後の発展として電源周波数を高周波化すれば,その問題も解決可能である。ダイオードの接合容量と挿入するインダクタとの共振周波数を入力電源周波数に近づけるように設計し,出力電圧のピークを観測する。

LC 共振の原理について説明する。通常, 共振回路の原理として, 周波数可変時のインピーダンスから入出力特性が議論される。しかしながら, 本論文で対象とする回路には, ダイオードが数多く含まれており, これまでの方法での説明は困難である。そこで, 電荷の移動という概念を用いることで, 入出力特性を議論することにする。

まず説明のため、負荷抵抗 R は充分に大きく、開放とみなす。 Fig. 3 に示すように、CW 回路のダイオードは偶数番が順次導通し、奇数番が常に非導通になっている。また、入力電流が反転する際には、その逆の動作を行なう。そのため、 $i_{\rm in}>0$  のときに、奇数番のダイオードの接合容量に電荷が充電され、 $i_{\rm in}<0$  のときに、偶数番のダイオードの接合容量に電荷が充電される。C が充分大きく、変動が微小だと仮定すると、交流のみを抽出した回路としては、Fig. 4の  $C_i$  を短絡させた回路と等価になる。そのため、ダイオードの接合容量を 10 個並列に接続されているようにみえる。提案回路で挿入した L と  $10C_T$  の直列回路となるため、LC 共振が生じると考えている。

さらに、LC 共振による昇圧比向上のメカニズムを電荷の移動の観点から考察する。共振時に入力電流電圧の位相が完全に一致し、入力から流れる電荷が、ダイオードの接合容量に充電される電荷と負荷抵抗に流れる電荷であると仮定する。その一周期 T=1/f における電荷の関係式が以下の通りである。

$$\int_0^T |i_{\rm in}| \, \mathrm{d}t = 10C_{\rm T} \cdot \frac{V_{\rm out}}{5} + \frac{V_{\rm out}}{R} \cdot T \cdot \cdots \cdot (4)$$

ここで,  $i_{\rm in}=I_{\rm in}\sin 2\pi ft$  として代入すると, 振幅  $I_{\rm in}$  は以下のようになる。

$$I_{\rm in} = 2\pi C_{\rm T} f V_{\rm out} + \frac{\pi V_{\rm out}}{R} \cdot \dots (5)$$

さらに、入出力電力が等しいと仮定すると、 $V_{\rm in}I_{\rm in}/2=V_{\rm out}^2/R$ という関係式が得られる。この関係式に  $I_{\rm in}$  を代入して、 $\alpha$ を求める。

$$\alpha = \frac{V_{\text{out}}}{V_{\text{in}}} = \pi C_{\text{T}} R f + \frac{\pi}{2} \cdots (6)$$

ここで、 $C_T = 30 \,\mathrm{pF}$ ,  $f = 100 \,\mathrm{kHz}$ ,  $R = 1 \,\mathrm{M}\Omega$  を代入すると、 $\alpha = 11 \,\mathrm{e}$ とり、従来 CW 回路よりも昇圧比が高くなる。

### 3. シミュレーション結果

本章では、数値計算によるシミュレーション結果について述べる。Fig. 5 の回路を LTspice 上で作成し、挿入する

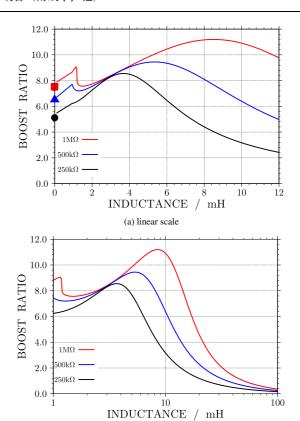

(b) logarithmic scale Fig. 6.  $\alpha$ -L characteristics in numerical calculations.

インダクタLの値と昇圧比 $\alpha$ の関係を数値的に求める。そして、 $\langle 2\cdot 3 \rangle$ 節で述べた昇圧比の向上を検討する。

Fig. 6 にシミュレーション結果を示す。Fig. 6(a) は横軸を均等目盛りに、Fig. 6(b) は横軸を対数目盛りにしている。ここで、負荷抵抗 R は 1 M $\Omega$ 、500 k $\Omega$ 、250 k $\Omega$  の 3 種類を用いている。また比較のため、Fig. 6(a) の L=0 mH の点は、従来の CW 回路における結果を示している。

Fig. 6 の結果において、どの抵抗値のときにも従来の結 果  $(L=0\,\mathrm{mH})$  の結果に比べて昇圧比が上昇していること が分かる。特に、挿入したインダクタの値により昇圧比の ピークが現れている。これは、インダクタの値が調整され て LC 共振の周波数が電源周波数に近づいているからであ ると考えられる。実際、ダイオードのデータシートから $C_{\rm T}$ は  $10\sim30$  pF の値である。 $\langle 2\cdot2\rangle$  節で述べたように、ダイ オードの接合容量による容量成分は、 $10C_T$ として現れる。 LC 共振の周波数  $f_r = 1/(2\pi\sqrt{L\cdot 10C_T})$  に,  $L = 8.2 \,\mathrm{mH}$ ,  $C_T = 30 \,\mathrm{pF}$  として概算すると,  $f_r = 101.5 \,\mathrm{kHz}$  となり, 電 源周波数の 100 kHz とほぼ等しい値となっていることが分 かる。したがって、Fig.6 の昇圧比のピークが LC 共振の 影響であると言える。そして、負荷抵抗の値が小さくなる にしたがって、ピークが下がりLの値が小さい方へシフト することも LC 共振の特徴と一致している。Fig. 6(b) に注 目すると, LC 共振を越えたインダクタの値では, 昇圧比 が急激に減少している。これは、共振周波数  $f_r$  が電源周波 数  $f = 100 \, \text{kHz}$  を下回ったからであると考えられる。次に、

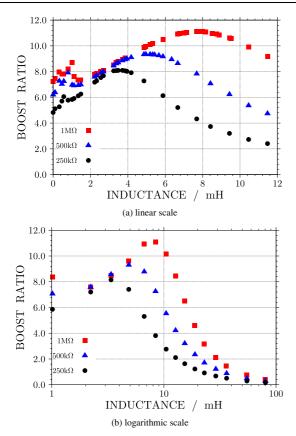

Fig. 7.  $\alpha$ -L characteristics in experimental system.

$L=1\,\mathrm{mH}$  付近の小さなピークについて考察する。 $\mathrm{mode}\ 6$  のように 2 直列のコンデンサによる共振であれば,共振周 波数  $f_\mathrm{r}=1/2\pi\,\sqrt{L\cdot(C/2)}\approx 103.8\,\mathrm{kHz}$  であり,電源周波数  $f=100\,\mathrm{kHz}$  と近い値になっていることが分かる。したがって,回路を構成するコンデンサと挿入したインダクタLの 共振であると推察される。

#### 4. 実証実験結果

本章では、前章で示したシミュレーション結果を実機によって実証する。実験において、高速バイポーラ電源(エヌエフ回路設計ブロック社製、HSA4051)を用いることで、これまでと同様のパラメータを設定する。Fig. 7 に挿入するインダクタを変化させたときの昇圧比の実験結果を示す。前章と同様、Fig. 7(a) は横軸を均等目盛りに、Fig. 7(b) は横軸を対数目盛りにしている。ここで、負荷抵抗 R は 1 M $\Omega$ 、500 k $\Omega$ 、250 k $\Omega$  の 3 種類を用いている。また比較のため、Fig. 7(a) の L = 0 mH の点は、従来の CW 回路における結果を示している。

Fig. 7 と前章の Fig. 6 を比較すると,定性的に結果が一致していることが分かる。昇圧比のピーク値はそれぞれ,  $(R=1\,\mathrm{M}\Omega,\ L=8.3\,\mathrm{mH})$  のとき, $\alpha=11$ , $(R=500\,\mathrm{k}\Omega,\ L=4.7\,\mathrm{mH})$  のとき, $\alpha=9.2$ , $(R=250\,\mathrm{M}\Omega,\ L=3.3\,\mathrm{mH})$  のとき, $\alpha=8.1\,\mathrm{E}$ いう結果が得られた。さらに,微小ながら  $(R=1\,\mathrm{M}\Omega,\ L=1.0\,\mathrm{mH})$  のときにインダクタ L と 10 個のコンデンサ  $C_1\sim C_{10}$  の共振も確認できる。

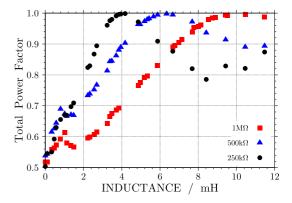

Fig. 8. TPF-L characteristics in experimental system.

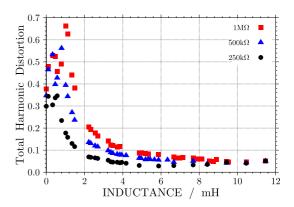

Fig. 9. THD-*L* characteristics in experimental system.

次に力率 (TPF) と入力電流  $i_{\rm in}$  の全高調波歪み (THD, Total Harmonic Distortion) について検証する。Fig. 8 と Fig. 9 に実験結果を示す。まず,Fig. 8 に注目する。従来の CW 回路では,力率が  $50\%\sim55\%$ である。提案回路の結果では, LC 共振付近において,力率 95%以上を達成している。続いて,Fig. 9 の THD に注目する。従来の CW 回路では,THD が  $30\%\sim40\%$ であるが,TPF と同様に,LC 共振付近において,THD が 10%以下という結果が得られている。また,L=1 mH 付近では,前述した L と C との共振により,電流波形が歪んでいるため,従来よりも THD が増加していると考えられる。以上の結果より,〈 $2\cdot3$ 〉節で述べたインダクタを挿入する効果が現れていることを実証した。

最後に、従来の結果である Fig. 2 と提案回路の入力電流を比較する。Fig. 10 に、 $R=250\,\mathrm{k}\Omega$ 、 $L=3.9\,\mathrm{mH}$  のときの入力電流電圧波形を示す。この結果からも、電圧電流が同位相になり、電流がほぼ正弦波になっていることが確認できる。

#### **5.** おわりに

本論文では、CW 回路における昇圧比の向上および力率の改善を目的とした回路を提案し、シミュレーションと実験からその妥当性を検証した。改善回路は、挿入したインダクタとダイオードの接合容量の共振を利用したものであり、その共振周波数が電源周波数と一致することも確認した。その結果、昇圧比を減少させる原因であるダイオード

Fig. 10. Input current and voltage waveforms in Fig. 5.

の接合容量をあえて利用することによって、昇圧比の向上 および力率の改善が達成された。ダイオードの接合容量を LC 共振に用いて、Lを可変させた特性について評価した が、一般的な周波数可変の特性も今後検討していく。さら に本論文では、出力容量が数 W 程度の実証実験であった が、実用回路を想定して、今後は大容量化を検討する予定 である。

#### 謝辞

本研究の一部は、パワーアカデミー研究助成により実施 されたものである。

#### 文 献

- (1) 守屋一成・丹羽章雅・茂木進一・枡川重男・勝嶋 肇:「燃料を利用 する創エネシステムとその電力変換回路技術」、平成 25 年電学産業 応用部門大会、I-S9-2 (2013)

- (2) 入江寿一・寺園勝志・松井景樹・安部征哉・斉藤亮治・米森秀登: 「高昇圧比を実現できる電力変換回路」、平成 25 年電学産業応用部門 大会、I-S9-5 (2013)

- (3) J.D. Cockcroft and E.T.S. Walton: "Experiments with High Velocity Positive Ions. (I) Further Developments in the method of obtaining High Velocity Positive Ions", Proceedings of the Royal Society of London. Series A, Vol.131, pp.619–630 (1932)

- (4) M. Yasubayashi, K. Matsui, E. Oishi, M. Umeno, H. Uchida, Y. Kawata, and M. Hasegawa: "Novel Voltage Equalizers for Secondary Batteries including EDLCs using CW circuit", Proceedings of the 3rd International Conference on Industrial Engineering 2015, pp.531–536 (2015)

- (5) A. Iijima, T. Hakamada, S. Matsui, and K. Kanaya: "DC High-Voltage Power Supply Molded by Epoxy Resin for Electron Beam Equipment", Bulletin of the Electrotechnical Laboratory, Vol.33, No.11, pp.1351–1365 (1969)

- (6) Y. Takamura: "A Cockcroft-Walton Circuit Analysis by Newly Developed Graphical Methods", *IEEJ Trans. EIS*, Vol.106, No.7, pp.119–126 (1986) (in Japanese) 高村芳雄:「図式解析法を用いたコッククロフト・ウォルトン回路の動作解析」, 電学論 C, Vol.106, No.7, pp.119–126 (1986)

- (7) E. Everhart and P. Lorrain: "The Cockcroft-Walton Voltage Multiplying Circuit", The Review of Scientific Instruments, Vol.24, No.3, pp.221–226 (1953)

- (8) 中西俊貴・大向 優・石飛 学・細田健一・伊東 毅:「コッククロフト・ウォルトン回路の減衰抑制に関する研究」,パワーエレクトロニクス学会講演資料, Vol.35, No.38, p.208 (2010)

- (9) H.R. Zinage and S.G. Gollagi: "Performance Analysis of Symmetric Multistage Voltage Multiplier", Journal of Engineering and Technology, Vol.1, pp.37–42 (2011)

- (10) C.-M. Young, M.-H. Chen, T.-A. Chang, C.-C. Ko, and K.-K. Jen: "Cascade Cockcroft-Walton Voltage Multiplier Applied to Transformerless High Step-up DC-DC Converter", IEEE Transactions on Industrial Electronics, Vol.60, No.2, pp.523–537 (2013)

- (11) T. Fukuyama and K. Sugihara: "Operating Principle of Cockcroft-Walton Circuit to Produce High-Voltage", The Papers of Technical Meeting, IEEJ, PST-13-089 pp.19–23 (2013) 福山隆雄・杉原慶一:「高電圧発生コッククロフト・ウォルトン回路 の動作原理」, ブラズマ研究会資料, Vol.13, No.89, pp.19–23 (2013)

- (12) M. Minami, T. Ito, S. Motegi, and M. Michihira: "Theoretical Analysis of Decreased Boost Ratio in Unloaded Cockcroft-Walton Circuit", *IEEJ Trans. IA*, Vol.136, No.3, pp.246–247 (2016) (in Japanese) 南 政孝・伊藤健・茂木進一・道平雅一:「無負荷 Cockcroft-Walton 回路における昇圧比減少の理論的解明」、電学論 D, Vol.136, No.3, pp.246–247 (2016)

- (13) 伊藤 健・南 政孝・茂木進一・道平雅一:「LC 共振を用いた Cockcroft-Walton 回路における負荷特性の実験的検討」、平成 28 年電気学会全 国大会論文集、4-108, p.184 (2016)

- (14) J.G. Kassakian, M.F. Schlecht, and G.C. Verghese: "Principles of Power Electronics 1st Edition", Prentice Hall, p.46 (1991)

南 政 孝 (正員) 1985年11月9日生。2010年3月京都

大学大学院工学研究科電気工学専攻修士課程修了。 2013 年 3 月同大学大学院工学研究科電気工学専攻博士後期課程修了。博士(工学)。2013 年 4 月神戸市立工業高等専門学校助教。2014 年 4 月講師,現在に至る。パワーエレクトロニクスに関する教育・研究に従事。電子情報通信学会,システム制御情報学会各会員。

伊 藤 健 (准員) 1995年9月11日生。2016年3月神戸

(准員) 1995年9月11日生。2016年3月7年 市立工業高等専門学校電気工学科卒業。同年4月 長岡技術科学大学工学部電気電子情報工学課程3 年次に編入し,現在に至る。電気学会関西支部平成27年度高専卒業研究発表会論文発表賞を受賞。

茂 木 進 一 (正員) 1971 年 7 月 29 日生。1996 年東京電機

大学大学院理工学研究科応用電子工学専攻修了。 1999 年同大学院理工学研究科応用システム工学 専攻満期退学。同年同大学理工学部電子情報工学 科助手,2003 年ヤンマー(株)入社,2012 年東 京電機大学工学部電気電子工学科研究員を経て, 2013 年神戸市立工業高等専門学校電気工学科准 教授,2016 年 4 月教授,現在に至る。博士(工

学)。パワーエレクトロニクスに関する教育・研究に従事。パワーエレクトロニクス学会,電子情報通信学会,電気設備学会各会員。

道 平 雅 一 (正員) 1969年12月3日生。1995年3月神戸

大学大学院工学研究科電気工学専攻修士課程修了。 1998年3月大阪大学大学院工学研究科電気工学 専攻博士後期課程修了。博士(工学)。同年4月 神戸市立工業高等専門学校電気工学科助手,1999 年4月講師,2002年4月助教授,2011年4月 教授,現在に至る。パワーエレクトロニクス回路 方式,システム制御に関する研究・教育に従事。

IEEE,パワーエレクトロニクス学会各会員。